在毫米波通信、相控阵雷达等高频电子系统中,陶瓷基板凭借其优异的介电稳定性与热管理能力,成为承载高频电路的核心材料。然而,表面金属化工艺的选择与执行精度,直接决定了信号传输的完整性与系统可靠性。本文从高频传输的物理本质出发,解析镀层粗糙度、导电特性、界面稳定性等关键参数的作用机制,结合实验数据与工程案例,为陶瓷基板表面处理提供科学决策依据。

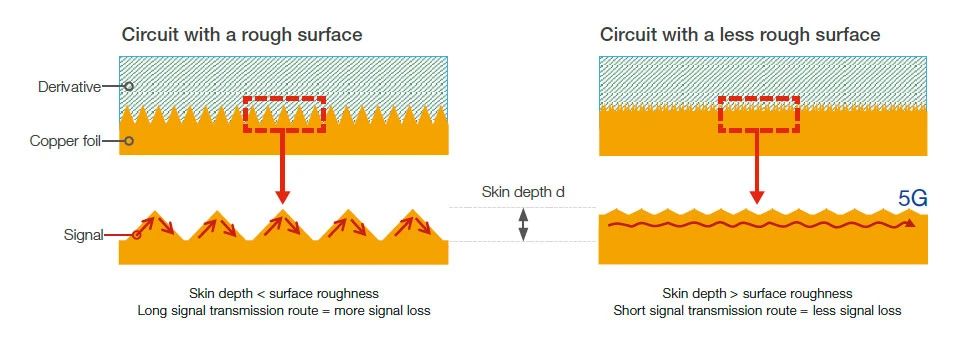

高频传输时陶瓷基板导体表面粗糙度越小,损耗也越小

高频电流因趋肤效应被强制约束在导体表层极薄区域,这一现象可由趋肤深度公式量化:

其中导体电阻率(ρ)、频率(f)、磁导率(μ)共同决定了电流渗透能力。以金为例,其在10 GHz下的趋肤深度为0.82 μm,至60 GHz时骤降至0.33 μm。这意味着当镀层厚度不足或表面存在微观缺陷时,电流将穿透高导电层进入底层材料,引发附加损耗。例如,化学镀金(ENIG)工艺中镍磷层(ρ=70 μΩ·cm)的电阻率是纯金的35倍,当金层厚度仅为0.3 μm时,60 GHz信号的实际电流路径有40%分布于镍磷层,导致插入损耗增加2.1 dB/cm。

表面粗糙度对趋肤效应的放大作用同样不可忽视。根据IEEE微波理论与技术协会的实测数据(2021),Ra从0.1 μm增至0.5 μm时,40 GHz传输线的导体损耗上升约18%。这一现象在毫米波频段尤为显著——某77 GHz汽车雷达模块采用磁控溅射镀金(Ra=0.05 μm)替代化学镀金后,信号衰减降低22%,相位一致性改善15%。

金属镀层的选择需在导电性、抗氧化性与加工成本间取得平衡。银(ρ=1.6 μΩ·cm)虽具有最优导电性能,但易与硫化物反应生成高阻层;金(ρ=2.2 μΩ·cm)的化学惰性使其成为高频场景的首选,但其成本限制了大规模应用;铜(ρ=1.7 μΩ·cm)作为折中方案,需通过表面镀金或钯层防止氧化。Rogers公司的对比实验表明:在28 GHz频段,铜-金复合镀层(铜厚5 μm+金厚0.5 μm)的插入损耗比纯金层低0.3 dB/cm,同时材料成本下降40%。

同时,镀层的热稳定性对高频系统可靠性至关重要。化学镀金工艺中镍磷层与陶瓷基板的热膨胀系数(CTE)失配可达7×10⁻⁶/K,在温度循环中产生微裂纹。某卫星通信载荷的失效分析显示,经历200次的-55℃~125℃温度循环后,ENIG镀层的微裂纹密度达到120条/mm²,导致阻抗失配率上升至8%。而采用溅射钛/金结构的样品在同等测试条件下,裂纹密度仅为3条/mm²,阻抗波动控制在±1.5%以内。

化学镀金工艺中常见的“黑盘”(Black Pad)缺陷,源于镀液对镍层的过度腐蚀。扫描电镜观测显示,黑盘区域的磷含量高达18 wt%,形成局部绝缘区,电阻率较正常区域提升50倍。在24 GHz频段,直径10 μm的黑盘缺陷可使回波损耗恶化至-12 dB,相当于信号反射功率达到6.3%。某5G基站滤波器因黑盘缺陷导致带内纹波超标,后期采用飞秒激光修复使良率提升至99.6%,但单件处理成本增加30%。

镀层厚度不均引发的阻抗失配同样不容小觑。当镀层厚度偏差超过±10%时,特性阻抗偏离设计值(如50 Ω),产生信号反射。以某毫米波连接器为例,化学镀金的厚度波动为±25%,导致阻抗一致性仅为±7 Ω;而物理气相沉积(PVD)工艺将厚度波动压缩至±3%,阻抗一致性提升至±1.2 Ω,电压驻波比(VSWR)从1.35优化至1.08。表面镀覆工艺对陶瓷基板高频性能的影响,本质上是电磁场、热力学、材料化学等多学科规律的交叉作用,工艺设计时需摒弃“经验驱动”的传统思维,增加从趋肤深度、界面态密度、晶格匹配度等微观维度进行思考。更多陶瓷基板的相关性能可以咨询深圳市晶瓷精密科技有限公司,晶瓷有着多年陶瓷基板金属化加工的行业技术经验,先进设备、专业团队、品质可靠,值得信赖!